ger_kar писал(а):Точнее может он есть, но не именно на этих выводах.

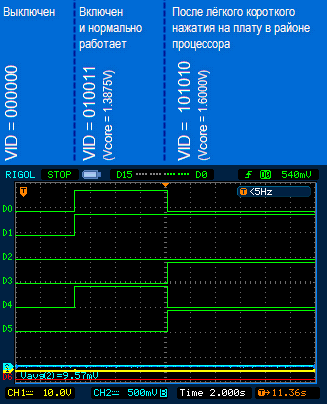

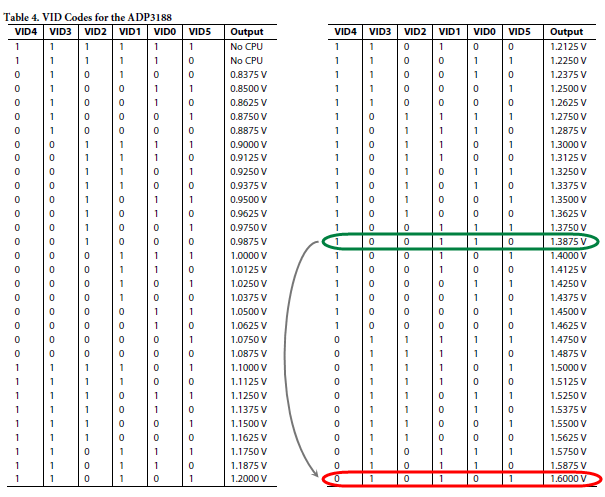

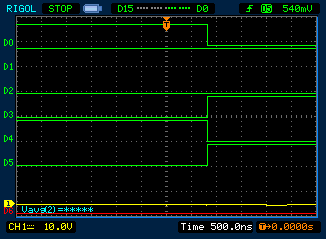

Ты не понимаешь. Когда-то была гипотеза, что пострадали именно VID-линии. Или что пострадало множество линий, и VID-линии просто входят в это множество. И что чаще всего причиной глюка является искажение VID-кода. И была мысль о лёгком способе фикса: жестко задать VID-код на входе VRM.

Теперь почти доказано, что перелома и КЗ самих VID-линий по всей видимости нет. О чём и сообщаю.

ger_kar писал(а):Питание зависит от процессора, а состояние процессора зависит от многих факторов и не обязательно отсутствие контакта должно быть на линиях контролера питания

Вот, а тут сразу интересный вопрос: зачем процессору на VID-выводах иметь опен-дрейны вместо жестко заданных перемычек на землю? Какую-то же цель это должно иметь, потому что это не то место, где лишние транзисторы приветствуются.

ger_kar писал(а):у процессора херова туча выводов

Это, конечно, легко так думать: мол, там же целых 775 всяких разных выводов, мало ли чего.

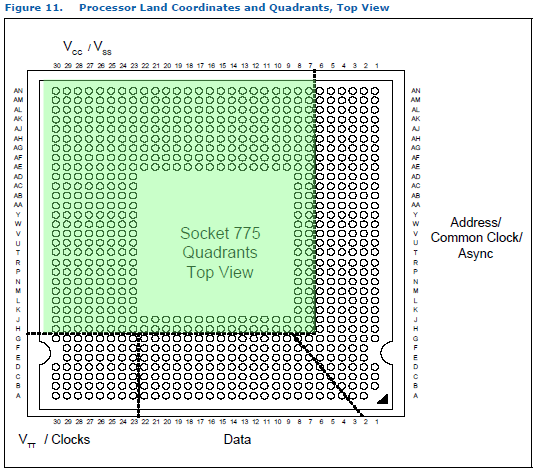

Но можно иметь немного больше смелости и тяги к установлению истины и пойти посмотреть распиновку LGA775. Я это сделал ещё 3 года назад. И прекрасно помню вот что: 80% от количества выводов — это вообще пины питания. В большом количестве, для способности пропускать большой ток. И отвал некоторых из них не меняет картину вообще.

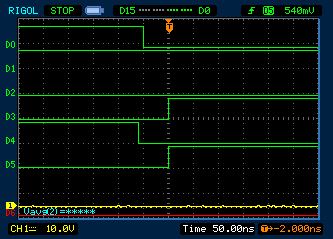

Вот картинка:

- lga775_ds_pinout_zones_1.png (37.42 Кб) Просмотров: 8628

Зелёный сектор — это всё куча параллельных пинов питания ядра. Отвал некоторых из них не может вызвать тот глюк, который происходит. Я скажу дальше больше: отвал всех из них никак не влияет на картину: я отключал от материнской платы коннектор, через который подаётся 12 вольт на VRM, процессор вообще не получал напряжение питания ядра, а глюк с искажением VID-пинов как был, так и остался и проявлялся точно так же. Так что исключаем пины питания ядра и всю ту логику внутри процессора, которая работает только когда это питание подаётся.

Если быть точнее: там 225 выводов VCC, 268 выводов VSS. И плюс 24 вывода VTT для терминирования лиший шины GTL+.

Итого 547 пинов чисто питающего характера.

А всего 775. 775 – 547 = остаётся 228.

18 пинов в документации отмечены как RESERVED. Остаётся 210.

30 пинов FC0...FC44, оставленные, как говорит даташит, для совместимости, и которые никуда не подключены. Остаётся 180.

64 пина 64-битной шины данных и 33 пина 36-битной (младших 3 битов нет, гранулярность адресации — 8 байт), итого 97 линий.

Я исключаю шину данных и адреса, потому что не могу представить себе сценарий, в рамках которого обрыв на шине данных или адреса заставит CPU перещёлкнуть внутри себя VID-код. Это не поддаётся логике. Более того, VID-ы перещёлкиваются даже тогда, когда ядро вообще не получает питания. И значит на шинных выводах процессора никакой активности быть не должно. А глюк есть. Поэтому шины я пока отметаю. Логика, отвечающее на прижимание VID-ов к земле, должна быть очень низкоуровневой, и начинать работу до того, как на ядро подано питание.

Остаётся 83 линии.

Ещё 13 линий тестовых линий TESTHI, которые должны быть терминированы на плате на VTT.

Остаётся 70 линий. Не 775, а всего-лишь 70.

Среди которых как интересные линии вроде выводов для PLL, выводы некоего базового питания процессора, так и неинтересные, типа A20-gate, локи, стробы, voltage-рефы для шины и т.п., группка линий для JTAG.

В общем, поломать голову над этими 70 линиями можно.

А не включать модель мышления «там же туча выводов, чё тут думать, перепаивать надо».

ger_kar писал(а):Проще пропаять сокет, как говориться или пан или пропал, но по любому хуже уже не будет.

Без флюса для BGA это имеет мало смысла, а его у меня сейчас нет, равно как и места и приспособ. Обычным феном от паяльной станции я не надеюсь прогреть достаточно плату для пропайки.

А хуже будет: сейчас плата заводит и работает, если её не трогать, до тех пор, пока какая-нибудь сильная вибрация не нарушит её покой. После неудачной перепайки первое включение может привести к тому, что погорят и испарятся дорожки, и вот тогда уже всё.