ger_kar –њ–Є—Б–∞–ї(–∞):–Ґ–Њ—З–љ–µ–µ –Љ–Њ–ґ–µ—В –Њ–љ –µ—Б—В—М, –љ–Њ –љ–µ –Є–Љ–µ–љ–љ–Њ –љ–∞ —Н—В–Є—Е –≤—Л–≤–Њ–і–∞—Е.

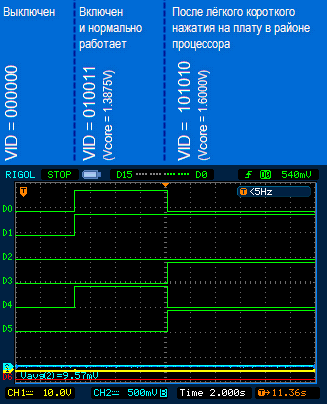

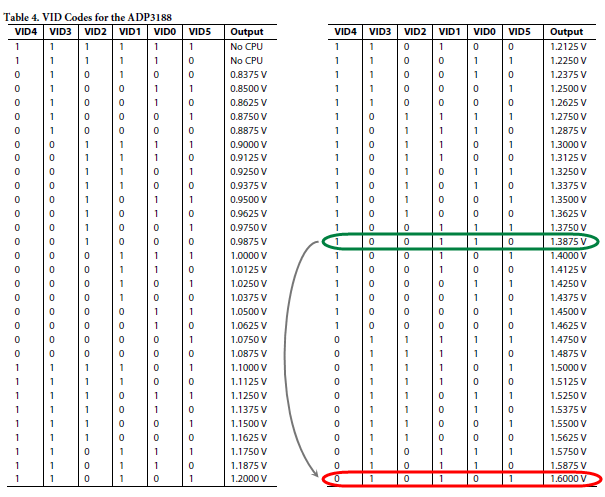

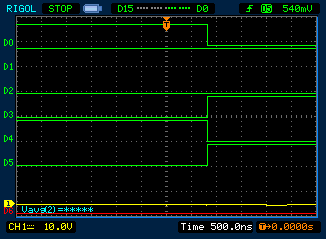

–Ґ—Л –љ–µ –њ–Њ–љ–Є–Љ–∞–µ—И—М. –Ъ–Њ–≥–і–∞-—В–Њ –±—Л–ї–∞ –≥–Є–њ–Њ—В–µ–Ј–∞, —З—В–Њ –њ–Њ—Б—В—А–∞–і–∞–ї–Є –Є–Љ–µ–љ–љ–Њ VID-–ї–Є–љ–Є–Є. –Ш–ї–Є —З—В–Њ –њ–Њ—Б—В—А–∞–і–∞–ї–Њ –Љ–љ–Њ–ґ–µ—Б—В–≤–Њ –ї–Є–љ–Є–є, –Є VID-–ї–Є–љ–Є–Є –њ—А–Њ—Б—В–Њ –≤—Е–Њ–і—П—В –≤ —Н—В–Њ –Љ–љ–Њ–ґ–µ—Б—В–≤–Њ. –Ш —З—В–Њ —З–∞—Й–µ –≤—Б–µ–≥–Њ –њ—А–Є—З–Є–љ–Њ–є –≥–ї—О–Ї–∞ —П–≤–ї—П–µ—В—Б—П –Є—Б–Ї–∞–ґ–µ–љ–Є–µ VID-–Ї–Њ–і–∞. –Ш –±—Л–ї–∞ –Љ—Л—Б–ї—М –Њ –ї—С–≥–Ї–Њ–Љ —Б–њ–Њ—Б–Њ–±–µ —Д–Є–Ї—Б–∞: –ґ–µ—Б—В–Ї–Њ –Ј–∞–і–∞—В—М VID-–Ї–Њ–і –љ–∞ –≤—Е–Њ–і–µ VRM.

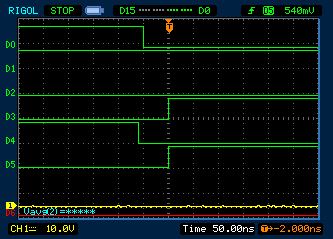

–Ґ–µ–њ–µ—А—М –њ–Њ—З—В–Є –і–Њ–Ї–∞–Ј–∞–љ–Њ, —З—В–Њ –њ–µ—А–µ–ї–Њ–Љ–∞ –Є –Ъ–Ч —Б–∞–Љ–Є—Е VID-–ї–Є–љ–Є–є –њ–Њ –≤—Б–µ–є –≤–Є–і–Є–Љ–Њ—Б—В–Є –љ–µ—В. –Ю —З—С–Љ –Є —Б–Њ–Њ–±—Й–∞—О.

ger_kar –њ–Є—Б–∞–ї(–∞):–Я–Є—В–∞–љ–Є–µ –Ј–∞–≤–Є—Б–Є—В –Њ—В –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞, –∞ —Б–Њ—Б—В–Њ—П–љ–Є–µ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –Ј–∞–≤–Є—Б–Є—В –Њ—В –Љ–љ–Њ–≥–Є—Е —Д–∞–Ї—В–Њ—А–Њ–≤ –Є –љ–µ –Њ–±—П–Ј–∞—В–µ–ї—М–љ–Њ –Њ—В—Б—Г—В—Б—В–≤–Є–µ –Ї–Њ–љ—В–∞–Ї—В–∞ –і–Њ–ї–ґ–љ–Њ –±—Л—В—М –љ–∞ –ї–Є–љ–Є—П—Е –Ї–Њ–љ—В—А–Њ–ї–µ—А–∞ –њ–Є—В–∞–љ–Є—П

–Т–Њ—В, –∞ —В—Г—В —Б—А–∞–Ј—Г –Є–љ—В–µ—А–µ—Б–љ—Л–є –≤–Њ–њ—А–Њ—Б: –Ј–∞—З–µ–Љ –њ—А–Њ—Ж–µ—Б—Б–Њ—А—Г –љ–∞ VID-–≤—Л–≤–Њ–і–∞—Е –Є–Љ–µ—В—М –Њ–њ–µ–љ-–і—А–µ–є–љ—Л –≤–Љ–µ—Б—В–Њ –ґ–µ—Б—В–Ї–Њ –Ј–∞–і–∞–љ–љ—Л—Е –њ–µ—А–µ–Љ—Л—З–µ–Ї –љ–∞ –Ј–µ–Љ–ї—О? –Ъ–∞–Ї—Г—О-—В–Њ –ґ–µ —Ж–µ–ї—М —Н—В–Њ –і–Њ–ї–ґ–љ–Њ –Є–Љ–µ—В—М, –њ–Њ—В–Њ–Љ—Г —З—В–Њ —Н—В–Њ –љ–µ —В–Њ –Љ–µ—Б—В–Њ, –≥–і–µ –ї–Є—И–љ–Є–µ —В—А–∞–љ–Ј–Є—Б—В–Њ—А—Л –њ—А–Є–≤–µ—В—Б—В–≤—Г—О—В—Б—П.

ger_kar –њ–Є—Б–∞–ї(–∞):—Г –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ —Е–µ—А–Њ–≤–∞ —В—Г—З–∞ –≤—Л–≤–Њ–і–Њ–≤

–≠—В–Њ, –Ї–Њ–љ–µ—З–љ–Њ, –ї–µ–≥–Ї–Њ —В–∞–Ї –і—Г–Љ–∞—В—М: –Љ–Њ–ї, —В–∞–Љ –ґ–µ —Ж–µ–ї—Л—Е 775 –≤—Б—П–Ї–Є—Е —А–∞–Ј–љ—Л—Е –≤—Л–≤–Њ–і–Њ–≤, –Љ–∞–ї–Њ –ї–Є —З–µ–≥–Њ.

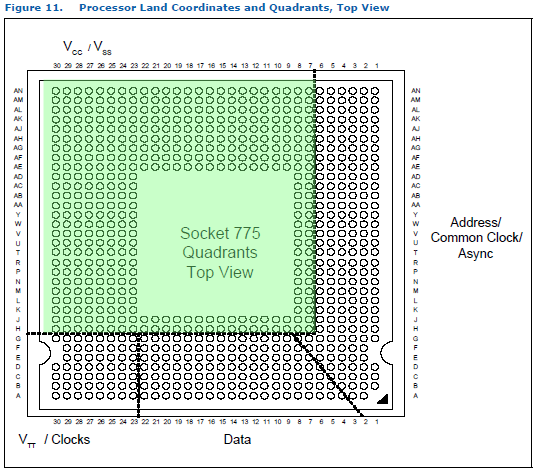

–Э–Њ –Љ–Њ–ґ–љ–Њ –Є–Љ–µ—В—М –љ–µ–Љ–љ–Њ–≥–Њ –±–Њ–ї—М—И–µ —Б–Љ–µ–ї–Њ—Б—В–Є –Є —В—П–≥–Є –Ї —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є—О –Є—Б—В–Є–љ—Л –Є –њ–Њ–є—В–Є –њ–Њ—Б–Љ–Њ—В—А–µ—В—М —А–∞—Б–њ–Є–љ–Њ–≤–Ї—Г LGA775. –ѓ —Н—В–Њ —Б–і–µ–ї–∞–ї –µ—Й—С 3 –≥–Њ–і–∞ –љ–∞–Ј–∞–і. –Ш –њ—А–µ–Ї—А–∞—Б–љ–Њ –њ–Њ–Љ–љ—О –≤–Њ—В —З—В–Њ: 80% –Њ—В –Ї–Њ–ї–Є—З–µ—Б—В–≤–∞ –≤—Л–≤–Њ–і–Њ–≤ вАФ —Н—В–Њ –≤–Њ–Њ–±—Й–µ –њ–Є–љ—Л –њ–Є—В–∞–љ–Є—П. –Т –±–Њ–ї—М—И–Њ–Љ –Ї–Њ–ї–Є—З–µ—Б—В–≤–µ, –і–ї—П —Б–њ–Њ—Б–Њ–±–љ–Њ—Б—В–Є –њ—А–Њ–њ—Г—Б–Ї–∞—В—М –±–Њ–ї—М—И–Њ–є —В–Њ–Ї. –Ш –Њ—В–≤–∞–ї –љ–µ–Ї–Њ—В–Њ—А—Л—Е –Є–Ј –љ–Є—Е –љ–µ –Љ–µ–љ—П–µ—В –Ї–∞—А—В–Є–љ—Г –≤–Њ–Њ–±—Й–µ.

–Т–Њ—В –Ї–∞—А—В–Є–љ–Ї–∞:

- lga775_ds_pinout_zones_1.png (37.42 –Ъ–±) –Я—А–Њ—Б–Љ–Њ—В—А–Њ–≤: 8456

–Ч–µ–ї—С–љ—Л–є —Б–µ–Ї—В–Њ—А вАФ —Н—В–Њ –≤—Б—С –Ї—Г—З–∞ –њ–∞—А–∞–ї–ї–µ–ї—М–љ—Л—Е –њ–Є–љ–Њ–≤ –њ–Є—В–∞–љ–Є—П —П–і—А–∞. –Ю—В–≤–∞–ї –љ–µ–Ї–Њ—В–Њ—А—Л—Е –Є–Ј –љ–Є—Е –љ–µ –Љ–Њ–ґ–µ—В –≤—Л–Ј–≤–∞—В—М —В–Њ—В –≥–ї—О–Ї, –Ї–Њ—В–Њ—А—Л–є –њ—А–Њ–Є—Б—Е–Њ–і–Є—В. –ѓ —Б–Ї–∞–ґ—Г –і–∞–ї—М—И–µ –±–Њ–ї—М—И–µ: –Њ—В–≤–∞–ї –≤—Б–µ—Е –Є–Ј –љ–Є—Е –љ–Є–Ї–∞–Ї –љ–µ –≤–ї–Є—П–µ—В –љ–∞ –Ї–∞—А—В–Є–љ—Г: —П –Њ—В–Ї–ї—О—З–∞–ї –Њ—В –Љ–∞—В–µ—А–Є–љ—Б–Ї–Њ–є –њ–ї–∞—В—Л –Ї–Њ–љ–љ–µ–Ї—В–Њ—А, —З–µ—А–µ–Ј –Ї–Њ—В–Њ—А—Л–є –њ–Њ–і–∞—С—В—Б—П 12 –≤–Њ–ї—М—В –љ–∞ VRM, –њ—А–Њ—Ж–µ—Б—Б–Њ—А –≤–Њ–Њ–±—Й–µ –љ–µ –њ–Њ–ї—Г—З–∞–ї –љ–∞–њ—А—П–ґ–µ–љ–Є–µ –њ–Є—В–∞–љ–Є—П —П–і—А–∞, –∞ –≥–ї—О–Ї —Б –Є—Б–Ї–∞–ґ–µ–љ–Є–µ–Љ VID-–њ–Є–љ–Њ–≤ –Ї–∞–Ї –±—Л–ї, —В–∞–Ї –Є –Њ—Б—В–∞–ї—Б—П –Є –њ—А–Њ—П–≤–ї—П–ї—Б—П —В–Њ—З–љ–Њ —В–∞–Ї –ґ–µ. –Ґ–∞–Ї —З—В–Њ –Є—Б–Ї–ї—О—З–∞–µ–Љ –њ–Є–љ—Л –њ–Є—В–∞–љ–Є—П —П–і—А–∞ –Є –≤—Б—О —В—Г –ї–Њ–≥–Є–Ї—Г –≤–љ—Г—В—А–Є –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞, –Ї–Њ—В–Њ—А–∞—П —А–∞–±–Њ—В–∞–µ—В —В–Њ–ї—М–Ї–Њ –Ї–Њ–≥–і–∞ —Н—В–Њ –њ–Є—В–∞–љ–Є–µ –њ–Њ–і–∞—С—В—Б—П.

–Х—Б–ї–Є –±—Л—В—М —В–Њ—З–љ–µ–µ: —В–∞–Љ 225 –≤—Л–≤–Њ–і–Њ–≤ VCC, 268 –≤—Л–≤–Њ–і–Њ–≤ VSS. –Ш –њ–ї—О—Б 24 –≤—Л–≤–Њ–і–∞ VTT –і–ї—П —В–µ—А–Љ–Є–љ–Є—А–Њ–≤–∞–љ–Є—П –ї–Є—И–Є–є —И–Є–љ—Л GTL+.

–Ш—В–Њ–≥–Њ 547 –њ–Є–љ–Њ–≤ —З–Є—Б—В–Њ –њ–Є—В–∞—О—Й–µ–≥–Њ —Е–∞—А–∞–Ї—В–µ—А–∞.

–Р –≤—Б–µ–≥–Њ 775. 775 вАУ 547 = –Њ—Б—В–∞—С—В—Б—П 228.

18 –њ–Є–љ–Њ–≤ –≤ –і–Њ–Ї—Г–Љ–µ–љ—В–∞—Ж–Є–Є –Њ—В–Љ–µ—З–µ–љ—Л –Ї–∞–Ї RESERVED. –Ю—Б—В–∞—С—В—Б—П 210.

30 –њ–Є–љ–Њ–≤ FC0...FC44, –Њ—Б—В–∞–≤–ї–µ–љ–љ—Л–µ, –Ї–∞–Ї –≥–Њ–≤–Њ—А–Є—В –і–∞—В–∞—И–Є—В, –і–ї—П —Б–Њ–≤–Љ–µ—Б—В–Є–Љ–Њ—Б—В–Є, –Є –Ї–Њ—В–Њ—А—Л–µ –љ–Є–Ї—Г–і–∞ –љ–µ –њ–Њ–і–Ї–ї—О—З–µ–љ—Л. –Ю—Б—В–∞—С—В—Б—П 180.

64 –њ–Є–љ–∞ 64-–±–Є—В–љ–Њ–є —И–Є–љ—Л –і–∞–љ–љ—Л—Е –Є 33 –њ–Є–љ–∞ 36-–±–Є—В–љ–Њ–є (–Љ–ї–∞–і—И–Є—Е 3 –±–Є—В–Њ–≤ –љ–µ—В, –≥—А–∞–љ—Г–ї—П—А–љ–Њ—Б—В—М –∞–і—А–µ—Б–∞—Ж–Є–Є вАФ 8 –±–∞–є—В), –Є—В–Њ–≥–Њ 97 –ї–Є–љ–Є–є.

–ѓ –Є—Б–Ї–ї—О—З–∞—О —И–Є–љ—Г –і–∞–љ–љ—Л—Е –Є –∞–і—А–µ—Б–∞, –њ–Њ—В–Њ–Љ—Г —З—В–Њ –љ–µ –Љ–Њ–≥—Г –њ—А–µ–і—Б—В–∞–≤–Є—В—М —Б–µ–±–µ —Б—Ж–µ–љ–∞—А–Є–є, –≤ —А–∞–Љ–Ї–∞—Е –Ї–Њ—В–Њ—А–Њ–≥–Њ –Њ–±—А—Л–≤ –љ–∞ —И–Є–љ–µ –і–∞–љ–љ—Л—Е –Є–ї–Є –∞–і—А–µ—Б–∞ –Ј–∞—Б—В–∞–≤–Є—В CPU –њ–µ—А–µ—Й—С–ї–Ї–љ—Г—В—М –≤–љ—Г—В—А–Є —Б–µ–±—П VID-–Ї–Њ–і. –≠—В–Њ –љ–µ –њ–Њ–і–і–∞—С—В—Б—П –ї–Њ–≥–Є–Ї–µ. –С–Њ–ї–µ–µ —В–Њ–≥–Њ, VID-—Л –њ–µ—А–µ—Й—С–ї–Ї–Є–≤–∞—О—В—Б—П –і–∞–ґ–µ —В–Њ–≥–і–∞, –Ї–Њ–≥–і–∞ —П–і—А–Њ –≤–Њ–Њ–±—Й–µ –љ–µ –њ–Њ–ї—Г—З–∞–µ—В –њ–Є—В–∞–љ–Є—П. –Ш –Ј–љ–∞—З–Є—В –љ–∞ —И–Є–љ–љ—Л—Е –≤—Л–≤–Њ–і–∞—Е –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –љ–Є–Ї–∞–Ї–Њ–є –∞–Ї—В–Є–≤–љ–Њ—Б—В–Є –±—Л—В—М –љ–µ –і–Њ–ї–ґ–љ–Њ. –Р –≥–ї—О–Ї –µ—Б—В—М. –Я–Њ—Н—В–Њ–Љ—Г —И–Є–љ—Л —П –њ–Њ–Ї–∞ –Њ—В–Љ–µ—В–∞—О. –Ы–Њ–≥–Є–Ї–∞, –Њ—В–≤–µ—З–∞—О—Й–µ–µ –љ–∞ –њ—А–Є–ґ–Є–Љ–∞–љ–Є–µ VID-–Њ–≤ –Ї –Ј–µ–Љ–ї–µ, –і–Њ–ї–ґ–љ–∞ –±—Л—В—М –Њ—З–µ–љ—М –љ–Є–Ј–Ї–Њ—Г—А–Њ–≤–љ–µ–≤–Њ–є, –Є –љ–∞—З–Є–љ–∞—В—М —А–∞–±–Њ—В—Г –і–Њ —В–Њ–≥–Њ, –Ї–∞–Ї –љ–∞ —П–і—А–Њ –њ–Њ–і–∞–љ–Њ –њ–Є—В–∞–љ–Є–µ.

–Ю—Б—В–∞—С—В—Б—П 83 –ї–Є–љ–Є–Є.

–Х—Й—С 13 –ї–Є–љ–Є–є —В–µ—Б—В–Њ–≤—Л—Е –ї–Є–љ–Є–є TESTHI, –Ї–Њ—В–Њ—А—Л–µ –і–Њ–ї–ґ–љ—Л –±—Л—В—М —В–µ—А–Љ–Є–љ–Є—А–Њ–≤–∞–љ—Л –љ–∞ –њ–ї–∞—В–µ –љ–∞ VTT.

–Ю—Б—В–∞—С—В—Б—П 70 –ї–Є–љ–Є–є. –Э–µ 775, –∞ –≤—Б–µ–≥–Њ-–ї–Є—И—М 70.

–°—А–µ–і–Є –Ї–Њ—В–Њ—А—Л—Е –Ї–∞–Ї –Є–љ—В–µ—А–µ—Б–љ—Л–µ –ї–Є–љ–Є–Є –≤—А–Њ–і–µ –≤—Л–≤–Њ–і–Њ–≤ –і–ї—П PLL, –≤—Л–≤–Њ–і—Л –љ–µ–Ї–Њ–µ–≥–Њ –±–∞–Ј–Њ–≤–Њ–≥–Њ –њ–Є—В–∞–љ–Є—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞, —В–∞–Ї –Є –љ–µ–Є–љ—В–µ—А–µ—Б–љ—Л–µ, —В–Є–њ–∞ A20-gate, –ї–Њ–Ї–Є, —Б—В—А–Њ–±—Л, voltage-—А–µ—Д—Л –і–ї—П —И–Є–љ—Л –Є —В.–њ., –≥—А—Г–њ–њ–Ї–∞ –ї–Є–љ–Є–є –і–ї—П JTAG.

–Т –Њ–±—Й–µ–Љ, –њ–Њ–ї–Њ–Љ–∞—В—М –≥–Њ–ї–Њ–≤—Г –љ–∞–і —Н—В–Є–Љ–Є 70 –ї–Є–љ–Є—П–Љ–Є –Љ–Њ–ґ–љ–Њ.

–Р –љ–µ –≤–Ї–ї—О—З–∞—В—М –Љ–Њ–і–µ–ї—М –Љ—Л—И–ї–µ–љ–Є—П ¬Ђ—В–∞–Љ –ґ–µ —В—Г—З–∞ –≤—Л–≤–Њ–і–Њ–≤, —З—С —В—Г—В –і—Г–Љ–∞—В—М, –њ–µ—А–µ–њ–∞–Є–≤–∞—В—М –љ–∞–і–Њ¬ї.

ger_kar –њ–Є—Б–∞–ї(–∞):–Я—А–Њ—Й–µ –њ—А–Њ–њ–∞—П—В—М —Б–Њ–Ї–µ—В, –Ї–∞–Ї –≥–Њ–≤–Њ—А–Є—В—М—Б—П –Є–ї–Є –њ–∞–љ –Є–ї–Є –њ—А–Њ–њ–∞–ї, –љ–Њ –њ–Њ –ї—О–±–Њ–Љ—Г —Е—Г–ґ–µ —Г–ґ–µ –љ–µ –±—Г–і–µ—В.

–С–µ–Ј —Д–ї—О—Б–∞ –і–ї—П BGA —Н—В–Њ –Є–Љ–µ–µ—В –Љ–∞–ї–Њ —Б–Љ—Л—Б–ї–∞, –∞ –µ–≥–Њ —Г –Љ–µ–љ—П —Б–µ–є—З–∞—Б –љ–µ—В, —А–∞–≤–љ–Њ –Ї–∞–Ї –Є –Љ–µ—Б—В–∞ –Є –њ—А–Є—Б–њ–Њ—Б–Њ–±. –Ю–±—Л—З–љ—Л–Љ —Д–µ–љ–Њ–Љ –Њ—В –њ–∞—П–ї—М–љ–Њ–є —Б—В–∞–љ—Ж–Є–Є —П –љ–µ –љ–∞–і–µ—О—Б—М –њ—А–Њ–≥—А–µ—В—М –і–Њ—Б—В–∞—В–Њ—З–љ–Њ –њ–ї–∞—В—Г –і–ї—П –њ—А–Њ–њ–∞–є–Ї–Є.

–Р —Е—Г–ґ–µ –±—Г–і–µ—В: —Б–µ–є—З–∞—Б –њ–ї–∞—В–∞ –Ј–∞–≤–Њ–і–Є—В –Є —А–∞–±–Њ—В–∞–µ—В, –µ—Б–ї–Є –µ—С –љ–µ —В—А–Њ–≥–∞—В—М, –і–Њ —В–µ—Е –њ–Њ—А, –њ–Њ–Ї–∞ –Ї–∞–Ї–∞—П-–љ–Є–±—Г–і—М —Б–Є–ї—М–љ–∞—П –≤–Є–±—А–∞—Ж–Є—П –љ–µ –љ–∞—А—Г—И–Є—В –µ—С –њ–Њ–Ї–Њ–є. –Я–Њ—Б–ї–µ –љ–µ—Г–і–∞—З–љ–Њ–є –њ–µ—А–µ–њ–∞–є–Ї–Є –њ–µ—А–≤–Њ–µ –≤–Ї–ї—О—З–µ–љ–Є–µ –Љ–Њ–ґ–µ—В –њ—А–Є–≤–µ—Б—В–Є –Ї —В–Њ–Љ—Г, —З—В–Њ –њ–Њ–≥–Њ—А—П—В –Є –Є—Б–њ–∞—А—П—В—Б—П –і–Њ—А–Њ–ґ–Ї–Є, –Є –≤–Њ—В —В–Њ–≥–і–∞ —Г–ґ–µ –≤—Б—С.